16+ verilog vector

Must contain at least 4 different symbols. PIC24F MCU and dsPIC33 DSC Applications.

Verilog Hdl

For example a 4-bit adder can be parameterized to accept a value for the number of bits and new parameter values can be passed in during module instantiation.

. For this purpose Verilog has scalar and vector net. Note that in line 16 N5 will override the default value of N ie. ASCII characters only characters found on a standard US keyboard.

Functional Safety with dsPIC33 DSCs and PIC24 MCUs. Y is an scalar reg array of depth12 each 1-bit wide wire 07 y2 30 y is an 8-bit. In this tutorial I am going to demonstrate different methods to generate a sinus wave in an FPGA with Verilog and VHDL.

Embedded Security With dsPIC33 DSCs and PIC24 MCUs. The verilog code below shows how we would do this using a generate for and a for loop. Advanced Sensor Interfacing With dsPIC33 DSCs.

Bit-level instruction-level data and task parallelismParallelism has long been employed in high. Num and den contain the coefficients of the numerator and denominator in descending powers of z. As an example lets look a very simple use case where we want to assign data to a 2 bit vector.

DsPIC33E DSCs - 70 MIPS. DsPIC33C DSCs - 100 MIPS. Although sometimes defined as an electronic version of a printed book some e-books exist without a printed equivalent.

Arrays are allowed in Verilog for reg wire integer and real data types. The circuit is structured just like a binary ripple-carry adder except the adders are base-10 rather than base-2. I d - v.

A single line comment starts with and tells Verilog compiler to treat everything after this point to the end of the line as a comment. PIC24F MCUs - 16 MIPS. Verilog needs to represent individual bits as well as groups of bits.

Download Mobirise Website Builder now and create cutting-edge beautiful websites that look amazing on any devices and browsers. So an N-bit adder can become a 4-bit 8-bit or 16-bit adder. Any number of dimensions can be created by specifying an address range after the identifier name and is called a multi-dimensional array.

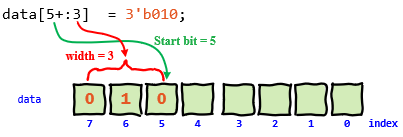

Fixed frequency variable frequency and a PWM sinusoidal signal. I have a custom module in Verilog that takes several inputs and a few parameters. 上一篇博文就说到了Verilog的数据类型其中就常用的就是reg类型以及wire类型这两种类型可以定义一位的变量也可以定义多位的变量其中一位称之为标量多位称之为向量类似于数组本篇博客主要讲述对多位变量的一些操作 例如 Verilog 2001修订版新增的bit位选择语法.

MOBIRISE WEB BUILDER Create killer mobile-ready sites. Num can be a vector or matrix while den must be a vector. This is going to be divided into 3 parts.

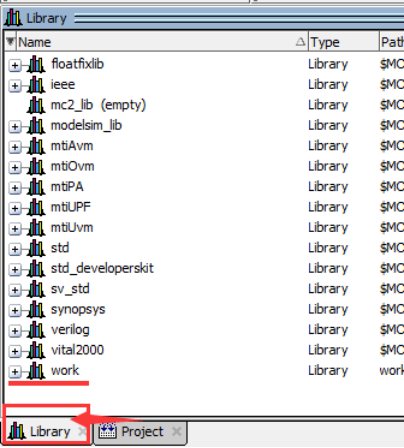

MPLAB Development Ecosystem and Software Tools. The difference between Verilog and VHDL will be explained in detail by examples. Contribute to pConstbasic_verilog development by creating an account on GitHub.

These operators compare two operands and return the result in a single bit 1 or 0. VLSI Design - Verilog Introduction Verilog is a HARDWARE DESCRIPTION LANGUAGE HDL. Parameters are Verilog constructs that allow a module to be reused with a different specification.

Its sometimes useful to only modify parts of a group of flip-flops. Create 16 D flip-flops. I am going to program and test the functionality with Vivado 20174.

Predefined VHDL data types include bit bit_vector string time boolean character and numeric real or integer. There are two ways to write comments in Verilog. In contrast when we use the normal for loop we are telling the verilog complier to create a single instance of the code block but execute it multiple times.

However a 16-bit sequential element is a register that can hold 16 bits. H b. Cnt cnt 116.

An ebook short for electronic book also known as an e-book or eBook is a book publication made available in digital form consisting of text images or both readable on the flat-panel display of computers or other electronic devices. The BCD representation for the 5-digit decimal number 12345 is 20h12345This is not the same as 14d12345 which is 14h3039. The preponed region is executed only once and is the first phase of current time slot after advancing the simulation timeSampling of signals from design for testbench input happens in this region.

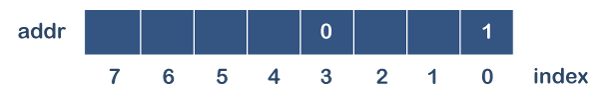

Reg or parameter vector with the use of. A 32-bit vector can be viewed as containing 4 bytes bits 3124 2316 etc. Verilog vs VHDL examples.

Verilog is case-sensitive so var_a and var_A are different. Java Vector 类Java 数据结构 Vector 类实现了一个动态数组和 ArrayList 很相似但是两者是不同的 Vector 是同步访问的 Vector 包含了许多传统的方法这些方法不属于集合框架 Vector 主要用在事先不知道数组的大小或者只是需要一个可以改变大小的数组的情况. An array declaration of a net or variable can be either scalar or vector.

Large problems can often be divided into smaller ones which can then be solved at the same time. Reverses signal order within multi-bit bus. Can count 0 thru 15.

Build a circuit that will reverse the byte ordering of the 4-byte word. Structural modeling is used in Line 9 where parameter mapping and port mapping is performed. Verilog code for 16-bit single cycle MIPS processor.

In line 5 a and b are defined as 4-bit vector. 6 to 30 characters long. In this project a 16-bit single-cycle MIPS processor is.

For example a single bit sequential element is a flip-flop. N2 in Listing 33. There are several different forms of parallel computing.

Would I then write wire 150 outputs 010. HDL Bits -- Verilog Practice. So then I would have a vector of elements of all_modA and the nth element of outputs would correspond to the nth instantiation of modA.

A multiple-line comment starts with and ends with and cannot be nested. The byte-enable inputs control whether each byte of the 16 registers should be written to on that cycle. Parallel computing is a type of computation in which many calculations or processes are carried out simultaneously.

Where m1 and n1 are the number of numerator and denominator coefficients respectively. Each output is a 16 bit wire. Resetn is a synchronous active-low reset.

The active region set consists of the following subregions Active Inactive and the NBA Nonblocking assignment regionsRTL code and. Specify the coefficients of the numerator. Reg30 b d h i count.

The order of the denominator must be greater than or equal to the order of the numerator. Byteena1 controls the upper byte d158 while byteena0 controls the lower byte d70. Added original DP RAM templates from Quartus and Vivado.

System Verilog 1 16 Youtube

Pdf 7 Elements Of Verilog Hdl Washington Vasquez Academia Edu

Numbers In Verilog Project F Fpga Dev

Hdl Verilog Vlsi Tutorial

Deal With The Complexity Of Vhdl Verilog And Systemverilog Sigasi

Air Supply Lab Lesson 04 Verilog Scalar Vector And Array

Full System Verilog Support Sigasi In The News Sigasi

Import Verilog Code And Generate Simulink Model Matlab Importhdl

![]()

How To Make Verilog Testbench Semiconductor Club

Verilog Code Github Topics Github

Verilog Scalar And Vector

Github Opentimer Parser Verilog A Standalone Structural Verilog Parser

Introduction To Verilog

How To Randomize A Queue In Systemverilog Quora

Hdl How To Write This For Loop Conditions In Verilog Design Correctly Stack Overflow

Verilog Scalar And Vector Javatpoint

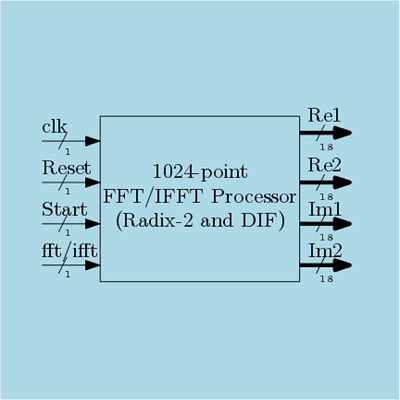

Verilog Code Of 1024 Point Fft Ifft Processor Digital System Design